Decode

The decode process turns the binary instruction streams into requests to the functional units.

Contents

Slots and Pipelines and Functional Units

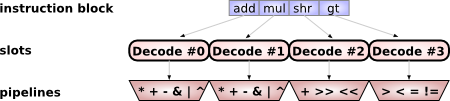

Each instruction is divided into blocks. Within those variable length blocks are the operations arranged in arrays. Each position in those arrays is called a Slot. It corresponds directly to a hardware slot, which is a pipeline of functional units where the actual work gets done, where the data is created, manipulated and shoveled around by operations.

Since there are two separate instruction streams, both are decoded by their respecitve specialized decoders. And not only each stream has it's own decoder, within each instruction, each block has its own specialized decoder. And each slot within each block has its own specialized binary operation format. This format depends on what functional units are available on the hardware pipeline this slot feeds into. Different hardware slots provide different functionality.

According to this different functionality the slots are grouped into a FlowCore and an ExuCore, each to serve its respective instruction streams, but this is a purely conceptual distinction.

There are no discreet modules or cores on the chip. There are only different Slots or pipelines arranged however is best.

Streams and Decoders

The decoders are distinct specialized modules though, each with their own data paths and caches and processing units to accomodate their specific work loads. The general format of the instruction streams is described under Encoding. Here we go into the details and see how those streams and instruciton formats are different.