Difference between revisions of "Decode"

(→Slots and Pipelines and Functional Units) | (→Streams and Decoders) | ||

| Line 18: | Line 18: | ||

The decoders are distinct specialized modules though, each with their own data paths and caches and processing units to accommodate their specific work loads. The general format of the instruction streams is described under [[Encoding]]. Here we go into the details and see how those streams and instruction formats are different. | The decoders are distinct specialized modules though, each with their own data paths and caches and processing units to accommodate their specific work loads. The general format of the instruction streams is described under [[Encoding]]. Here we go into the details and see how those streams and instruction formats are different. | ||

| + | |||

| + | ==== Morsels ==== | ||

| + | A morsel is the basic unit to encode values within the instruction stream. They take as many bits as are needed to address all belt locations on a specific [[Cores|core]], i.e. 3-5 bits.<br /> | ||

| + | In most instructions taking immediate values those immediates also are morsel-sized. | ||

=== Flow Stream === | === Flow Stream === | ||

Revision as of 23:17, 31 October 2014

The decode process turns the binary instruction streams into requests to the functional units.

Contents

Slots and Pipelines and Functional Units

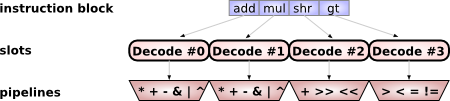

Each instruction is divided into blocks. Within those variable length blocks are the operations arranged in arrays. Each position in those arrays is called a slot. It corresponds directly to a hardware slot, which a dedicated decoder that can only decode the operations that can occur at this position in the instruction. The slot then sends a request to perform the decoded operation to the proper pipeline, or in some cases like the pick operation to the crossbar circuits.

A pipeline is a collection of functional units that share a common data path, the same inputs and outputs. It is in the functional units where the actual work gets done, where the data is manipulated and shoveled around by operations.

Since there are two separate instruction streams, both are decoded by their respective specialized decoders. And not only each stream has it's own decoder, within each instruction, each block has its own specialized decoder. And each slot within each block has its own specialized binary operation format. This format depends on what functional units are available on the hardware pipeline this slot feeds into. Different hardware slots provide different functionality.

According to this different functionality the slots are grouped into a FlowCore and an ExuCore, each to serve its respective instruction streams, but this is a purely conceptual distinction.

There are no discreet modules or cores on the chip. There are only different Slots and Pipelines arranged however is best.

Streams and Decoders

The decoders are distinct specialized modules though, each with their own data paths and caches and processing units to accommodate their specific work loads. The general format of the instruction streams is described under Encoding. Here we go into the details and see how those streams and instruction formats are different.

Morsels

A morsel is the basic unit to encode values within the instruction stream. They take as many bits as are needed to address all belt locations on a specific core, i.e. 3-5 bits.

In most instructions taking immediate values those immediates also are morsel-sized.