US010678700B2

# (12) United States Patent

### Godard et al.

## (54) CPU SECURITY MECHANISMS EMPLOYING THREAD-SPECIFIC PROTECTION DOMAINS

(71) Applicant: Mill Computing, Inc., Palo Alto, CA

(US)

(72) Inventors: Roger Rawson Godard, East Palo

Alto, CA (US); **Arthur David Kahlich**, Sunnvale, CA (US); **Jan Schukat**, Berlin (DE); **William Edwards**, Bräkne

Hoby (SE)

(73) Assignee: Mill Computing, Inc., Palo Alto, CA

(US)

(\*) Notice: Subject to any disclaimer, the term of this

patent is extended or adjusted under 35 U.S.C. 154(b) by 128 days.

(21) Appl. No.: 15/559,858

(22) PCT Filed: Mar. 21, 2016

(86) PCT No.: PCT/US2016/023420

§ 371 (c)(1),

(2) Date: Sep. 20, 2017

(87) PCT Pub. No.: WO2016/154115

PCT Pub. Date: Sep. 29, 2016

(65) Prior Publication Data

US 2018/0060244 A1 Mar. 1, 2018

### Related U.S. Application Data

(63) Continuation of application No. 14/663,760, filed on Mar. 20, 2015, now Pat. No. 9,747,218.

(Continued)

(51) Int. Cl.

G06F 12/08

(2016.01) (2016.01)

G06F 12/0893

(Continued)

(10) Patent No.: US 10,678,700 B2

(45) Date of Patent:

Jun. 9, 2020

(52) U.S. Cl.

(Continued)

(58) Field of Classification Search

CPC .... G06F 12/0875; G06F 12/0893; G06F 9/00; G06F 9/46; G06F 9/3004; G06F 9/3009;

(Continued)

(56) References Cited

U.S. PATENT DOCUMENTS

6,546,546 B1 4/2003 Van Doorn 6,604,123 B1 8/2003 Bruno et al.

(Continued)

FOREIGN PATENT DOCUMENTS

WO WO 2010/151267 A1 12/2010

OTHER PUBLICATIONS

Early Capability Architectures, Capability Based-Computer Systems, Henry M. Levy, 1984, pp. 41-47.

(Continued)

Primary Examiner — Pierre Miche Bataille

(74) Attorney, Agent, or Firm — Gordon & Jacobson,

P.C

(57) ABSTRACT

A computer processor includes an instruction processing pipeline that interfaces to a hierarchical memory system employing an address space. The instruction processing pipeline includes execution logic that executes at least one thread in different protection domains over time, wherein the different protection domains are defined by descriptors each including first data specifying a memory region of the address space employed by the hierarchical memory system and second data specifying permissions for accessing the associated memory region. The address space can be a virtual address space or a physical address space. The protection domains can be associated with different turfs (Continued)

each representing a collection of descriptors. A given thread can execute in a particular protection domain(turf), one protection domain (turf) at a time with the particular protection domain (turf) selectively configured to change over time.

## 32 Claims, 24 Drawing Sheets

## Related U.S. Application Data

- (60) Provisional application No. 62/145,070, filed on Apr. 9, 2015.

- (51) Int. Cl.

G06F 12/0875 (2016.01)

G06F 9/30 (2018.01)

G06F 12/14 (2006.01)

G06F 9/38 (2018.01)

G06F 9/46 (2006.01)

G06F 9/00 (2006.01)

- (58) **Field of Classification Search** CPC ... G06F 9/3802; G06F 9/3851; G06F 12/1441

| USPC                                     | 711/152, | 150 |

|------------------------------------------|----------|-----|

| See application file for complete search | history. |     |

## (56) References Cited

### U.S. PATENT DOCUMENTS

| 7,287,140 B1     | 10/2007 | Asanovic et al.        |

|------------------|---------|------------------------|

| 7,437,521 B1     | 10/2008 | Scott et al.           |

| 9,122,890 B2     | 9/2015  | Grocutt et al.         |

| 9,652,230 B2     | 5/2017  | Godard et al.          |

| 9,747,216 B2     | 8/2017  | Godard et al.          |

| 9,747,218 B2*    | 8/2017  | Godard G06F 12/0875    |

| 9,934,166 B2*    | 4/2018  | Wilkerson G06F 9/322   |

| 2005/0198479 A1  | 9/2005  | Bean et al.            |

| 2011/0276760 A1  | 11/2011 | Chou                   |

| 2012/0144167 A1* | 6/2012  | Yates, Jr G06F 9/30174 |

|                  |         | 712/216                |

| 2013/0275656 A1* | 10/2013 | Talagala G06F 12/0246  |

|                  |         | 711/103                |

| 2013/0283017 A1* | 10/2013 | Wilkerson G06F 9/322   |

|                  |         | 712/225                |

| 2014/0075581 A1  | 3/2014  | Grocutt et al.         |

| 2016/0350019 A1* | 12/2016 | Koufaty G06F 3/0622    |

| 2017/0232003 A1  | 8/2017  | Voskuhl                |

## OTHER PUBLICATIONS

Mondrian Memory Protection, Emmett Witchel et al., MIT Laboratory for Computer Science, 2002.

Mondrix: Memory Isolation for Linux Using Mondriaan Memory Protection, Emmett Witchel et al., 2005.

<sup>\*</sup> cited by examiner

Fetch — Decode — Issue — Execute — Retire FIG. 2

FIG. 3

FIG. 4

FIG. 5A

FIG. 5B

FIG. 5C

FIG. 6A

Logical Call Stack for Thread A (Chain of Stacklets)

FIG. 6C

# Portal Entry

|       |         |      |      |       | ٦ |

|-------|---------|------|------|-------|---|

| entry | Turf id | data | code | const |   |

FIG. 8A

# Stacklet Info Block

| TOS | base | limit |   |

|-----|------|-------|---|

|     |      |       | 1 |

FIG. 8B

**FIG. 10**

Jun. 9, 2020

US 10,678,700 B2

**FIG. 11**

**FIG. 12**

Jun. 9, 2020

**FIG. 13**

**FIG. 14A**

FIG. 14B

FIG. 17

FIG. 18

FIG. 19

FIG. 20

Jun. 9, 2020

FIG. 22

## CPU SECURITY MECHANISMS EMPLOYING THREAD-SPECIFIC PROTECTION DOMAINS

#### BACKGROUND OF THE INVENTION

### 1. Field

The present disclosure relates to computer processing systems.

### 2. State of the Art

A computer processor and the program which it executes needs places to put data for later reference. A computer 15 processor will typically have many such places, each with its own trade off of capacity, speed of access, and cost. Usually these are arranged in a hierarchal manner referred to as the memory system of the computer processing system, with small, fast, costly places used for short lived small data and 20 large, slow and cheap places used for what doesn't fit in the small, fast, costly places. The hierarchical memory system typically includes the following components arranged in order of decreasing speed of access:

a register file or other form of fast operand storage;

one or more levels of cache memory (one or more levels of the cache memory can be integrated with the processor (on-chip cache) or separate from the processor (off-chip cache):

main memory (or physical memory), which is typically 30 implemented by DRAM memory and/or NVRAM memory and/or ROM memory; and

on-line mass storage (typically implemented by one or more hard disk drives).

In many computer processing systems, the main memory 35 can take several hundred cycles to access. The cache memory, which is much smaller and more expensive but with faster access as compared to the main memory, is used to keep copies of data that resides in the main memory. If a reference finds the desired data in the cache (a cache hit) it 40 can access it in a few cycles instead of several hundred when it doesn't (a cache miss). Because a program typically has nothing else to do while waiting to access data in memory, using a cache and making sure that desired data is copied into the cache can provide significant improvements in 45 performance.

The address space of the program can employ virtual memory, which provides for two different purposes in modern processors. One purpose, hereinafter paging, permits the totality of the address spaces used by all programs to exceed 50 the capacity of the main memory attached to the processor. The other purpose, hereinafter address extension, permits the totality of the address spaces used by all programs to exceed the address space supported by the processor.

Paging can be used to map the virtual addresses used by 55 the program at page granularity to physical addresses recognized by the main memory or to devices such as disk that are used as paging store. The set of valid virtual addresses usable without error by a program is called its address space. The address mapping is represented by a set of mapping 60 tables maintained by the operating system as it allocates and de-allocates memory for the various running programs. Every virtual address must be translated to the corresponding physical address before it may be used to access physical memory.

Systems with caches differ in whether cache lines store tags defined by a physical address (physical caching) or a 2

virtual address (virtual caching). In the former, virtual addresses must be translated at least before they are used to match against the physical addressed tags of the cache; in the latter, translation occurs after cache access and is avoided if the reference is satisfied from cache.

Address extension is not needed when the space encompassed by the representation of a program address is large enough. Common representations of program address space are four bytes (32 bits) and eight bytes (64 bytes). The four-byte representation (yielding a four gigabyte address space) is easily exceeded by modern programs, so addresses (and address spaces) must be reused with different meanings by different programs and address extension must be used. Reuse of the same address by different programs is called aliasing. The computer processing system must disambiguate aliased use of addresses before they are actually used in the memory hierarchy.

In a computer processing system employing physical caching, alias disambiguation occurs prior to the caches. In a computer processing system employing virtual caching, disambiguation can occur after the caches if the caches are restricted to hold only memory from a single one of the aliased addressed spaces. Such a design requires that cache contents be discarded whenever the address space changes. However, the total space used by even thousands of very large programs will not approach the size representable in 64 bits, so aliasing need not occur and address extension is unnecessary in 64-bit machines. A computer processing system that does not use address extension permits all programs to share a single, large address space; such a design is said to use the single-address-space model.

It happens that the same hardware can be used both to disambiguate aliases and to map physical memory, and such is the common arrangement. Because alias disambiguation is typically performed prior to physical caches, using the common hardware means that page mapping occurs their too. When paging and alias disambiguation are in front of physical caches, it is also common to use the same hardware for access control, restricting the kinds of access and the addresses accessible to the program. The hardware enforced restrictions comprise the protection model of the processor and memory system. Protection must apply to cache accesses, so the protection machinery must be ahead of the caches. Hence it is common to have one set of hardware that intercepts all accesses to the memory hierarchy and applies protection restriction, alias disambiguation, and page mapping all together. Because all this must be performed for every reference to memory, and specifically must be performed before cache can be accessed, the necessary hardware is power hungry, large and on the critical path for program performance.

Furthermore, modern CPU architectures support protected multiprocessing where different program invocations are given their own sets of private resources (a process) and then run in parallel, with a combination of hardware and software ensuring that no program can inspect or change the private resources of any other. This protected multiprocessing is often accomplished by letting the CPU execute the code of one process for a while (with access to the resources of that process), and then changing the hardware execution environment to that of another process and running that one for a while with access to the resources of the second but no longer with access to the resources of the first. Changing from running one process to running another is called a process switch and is very expensive in machine terms because of the amount of state that has to be saved and restored as the process context is changed.

A process can contain multiple threads. A thread is a sequence of one or more instructions executed by the CPU. Typically, threads are used for small tasks, whereas processes are used for more heavyweight tasks, such as the execution of applications. Another difference between a 5 thread and a process is that threads within the same process share the same address space, whereas different processes do not. This allows threads to read from and write to the same data structures and variables, and also facilitates communication between threads.

Communication between processes (also known as interprocess communication) can be quite difficult and resourceintensive. For example, one process may be the source of some data that it computes or reads from a file, while the second is a sink for the data which it uses in its own 15 operation or writes out to a file in turn. In the usual arrangement, the processes arrange for a buffer to be created as a shared resource in memory that they both have access to. The source then fills the buffer with data and triggers a process switch to the sink. The sink consumes the data, and 20 then triggers a process switch back to the source for more data. Each buffer full thus involves two process switches. In addition, the processes must establish some protocol to make sure that (for example) the source doesn't start putting emptying it of the previous data. Such protocols are difficult to write and a frequent source of subtle bugs.

Communication between the threads of a process is much easier. In one method, both source and sink threads can run concurrently (on separate cores) or semi-concurrently (being 30 swapped in and out of a single core), and communicate using shared data structures similar to inter-process communication. In a second method, only one thread is active at a time (no matter how many cores are available), and a special operation or system function permits the running thread to 35 give up control to an idle thread, possibly passing arguments to the idle thread. This method is typically referred to as "coroutines," and the operation that stops the active thread and passes control to the idle thread is often called a "visit." Processes can also communicate as coroutines.

The difference between process and thread-based communication is that the threads share their whole environment, while processes don't, although they may share limited quantities of state for purposes of the communication. Thus, current CPU architectures require that the program 45 code of the cooperating source and sink threads share resource environments. If the code of the source and sink are to have private resource sets, they must be organized as separate processes and utilize the process switch machinery and a custom protocol.

### **SUMMARY**

This summary is provided to introduce a selection of concepts that are further described below in the detailed 55 description. This summary is not intended to identify key or essential features of the claimed subject matter, nor is it intended to be used as an aid in limiting the scope of the claimed subject matter.

Illustrative embodiments of the present disclosure are 60 directed to a computer processor including an instruction processing pipeline that interfaces to a hierarchical memory system employing an address space. The instruction processing pipeline includes execution logic that executes at least one thread in different protection domains over time, 65 wherein the different protection domains are defined by descriptors each including first data specifying a memory

region of the address space employed by the hierarchical memory system and second data specifying permissions for accessing the associated memory region. The address space can be a virtual address space or a physical address space. The protection domains can be defined by turfs each representing a collection of descriptors. A given thread can execute in a particular protection domain/turf, one protection domain/turf at a time. The particular protection domain/ turf can be selectively configured to change over time.

In one embodiment, the descriptors of a protection domain are associated with a key (turf ID) that identifies the protection domain. The protection domain can be associated with a key (thread ID) that uniquely identifies the thread that currently executes in the protection domain. The thread ID can have a configuration that specifies a wildcard identifier corresponding to any thread being executed by the execution logic. The turf ID can have a configuration that specifies a wildcard identifier corresponding to any turf being executed by the execution logic.

The descriptors can be stored in at least one hardware table that is queried in conjunction with servicing requests that access the hierarchical memory system.

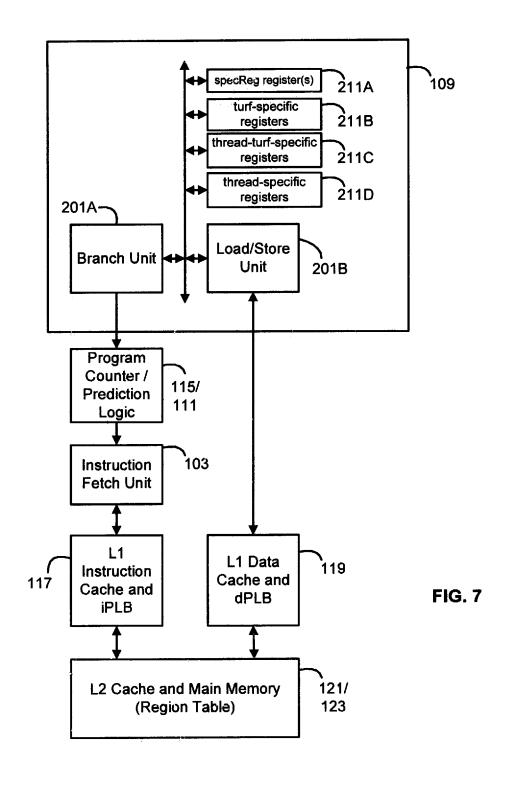

In one embodiment, the hierarchical memory system more data into the buffer before the sink has finished 25 includes a top level instruction cache separate from a top level data cache. The descriptors for memory regions that store instructions are stored in a first hardware table that is queried in conjunction with servicing fetch requests that are issued to the top level instruction cache for accessing instruction portions stored in the top level instruction cache. The descriptors for memory regions that store operand data are stored in a second hardware table that is queried in conjunction with servicing memory requests that are issued to the top level data cache for loading operand data from or storing operand data in the top level data cache. The second data for descriptors stored in the first hardware table can selectively specify an execute permission or a portal permission. The second data for descriptors stored in the second hardware table can selectively specify a write permission or 40 a read permission. Both tables can selectively specify a grant permission, which permits transitive re-granting. The first hardware table can be queried in parallel with querying the top level instruction cache, and the second hardware table can be queried in parallel with querying the top level data cache. These tables are known as the "persistent" tables, as opposed to the "transient" tables to be described later, and the permissions they contain are part of the "persistent permissions".

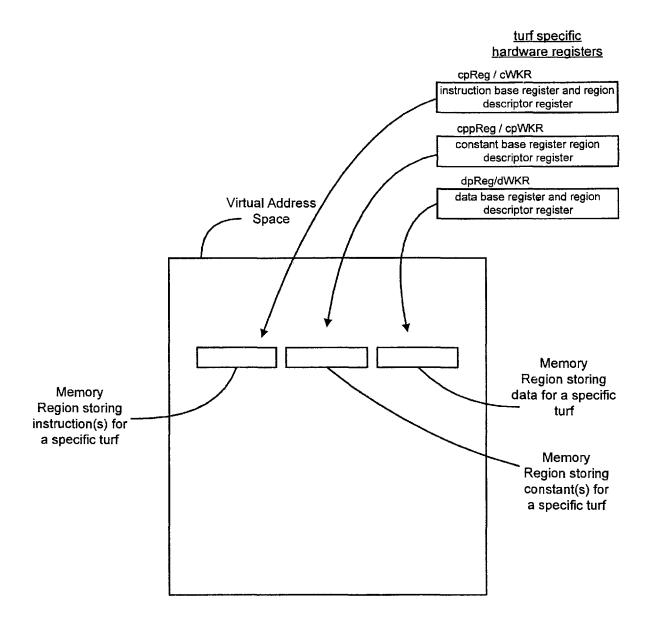

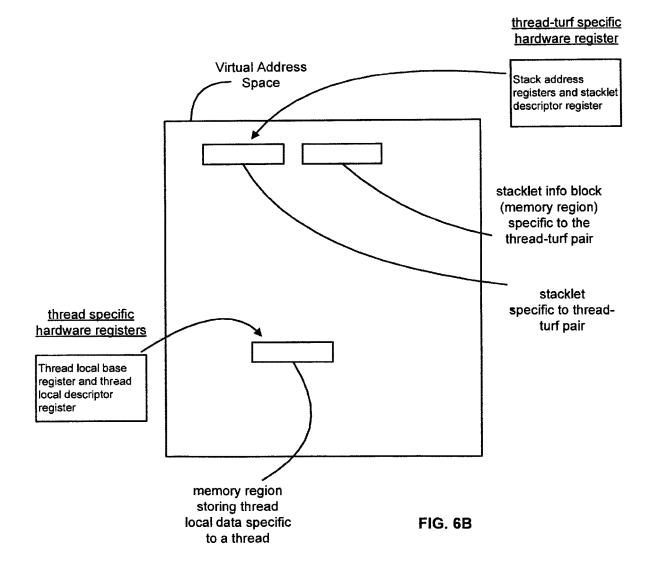

> In another embodiment, the protection domains can be 50 further defined by descriptors for predefined memory regions of the address space that are stored in hardware registers of the computer processor. The predefined memory regions can include at least one memory region selected from the group including: at least one turf-specific memory region, at least one thread-turf-specific memory region, and at least one thread-specific memory region. The at least one turf-specific memory region can include a first memory region that stores instructions for a particular turf, a second memory region that stores constants for a particular turf, and a third memory region that stores data for the particular turf. The at least one thread-turf-specific memory region can include a memory region that stores a stack portion for a particular thread-turf pair (e.g., a stack frame for the stacklet of the particular thread-turf pair as described herein). The at least one thread-specific memory region can include a memory region that stores thread local data for a particular thread. These hardware descriptors also comprise part of the

"persistent permissions". It is possible for permissions in the hardware descriptors and in the persistent tables to duplicate or overlap each other.

The hardware registers that store the descriptors for the predefined memory regions of the address space can be accessed and processed in order to perform protection checking before querying the at least one hardware table that stores the descriptors for protection checking. In certain circumstances, the protection checking carried out by accessing and processing the hardware registers that store the descriptors for the predefined memory regions of the address space avoids the protection checking carried out by accessing and processing the at least one hardware table that stores the descriptors.

The at least one hardware table storing the descriptors can be backed to one or more Permission Tables stored in the memory system. The descriptors can be stored as entries in the hardware table where each entry includes a single bit that is processed when first adding the corresponding entry to the 20 at least one hardware table and when evicting the corresponding entry from the at least one hardware table. Such processing can remove the corresponding entry from the at least one hardware table without accessing the one or more Permission Tables for circumstances when the correspond- 25 according to an embodiment of the present disclosure. ing entry is not located in the one or more Permission Tables.

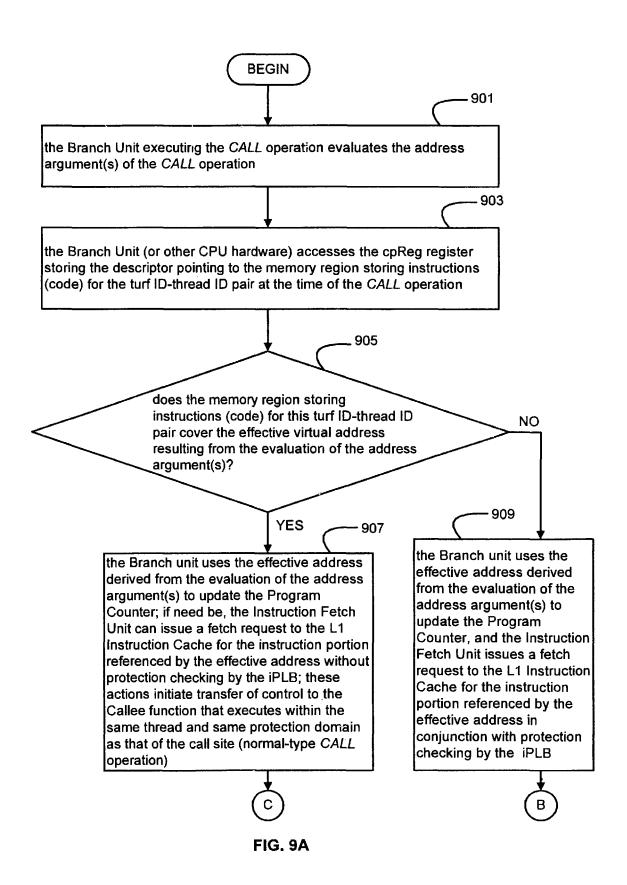

In still another embodiment, the first data of at least one descriptor specifies a memory region storing a portal associated with a particular function or service. The instruction processing pipeline can support a portal-type CALL opera- 30 tion with a pointer argument that refers to the portal. The actions of the portal-type CALL operation process the portal to switch to a different protection domain defined by the portal without switching threads. The portal can include a turf ID that refers to the different protection domain which 35 is used during execution of the particular function or service associated with the portal. The portal can also include address data that refers to the entry address of the particular function or service. The portal can also include state information that is restored to hardware registers for use during 40 execution of the particular function or service. The portal can act as indirect interface mechanism to the execution of the particular function or service.

In one embodiment, for the at least one descriptor that specifies a memory region storing the portal, the second data 45 of such descriptor includes a portal permission. The portal permission of the second data of such descriptor can be processed in conjunction with the execution of the portaltype CALL operation to distinguish the portal-type CALL operation from a normal-type CALL operation.

### BRIEF DESCRIPTION OF THE DRAWINGS

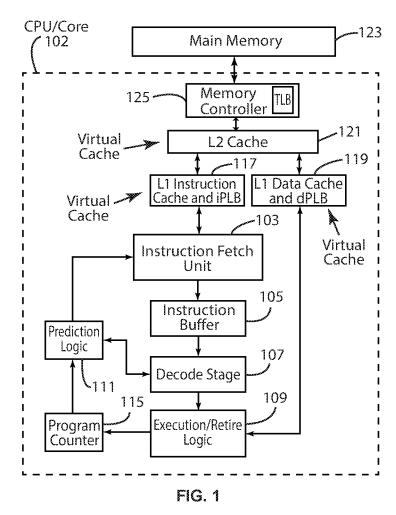

- FIG. 1 is a schematic block diagram of a computer processing system according to an embodiment of the pres- 55 ent disclosure.

- FIG. 2 is a schematic diagram of exemplary pipeline of processing stages that can be embodied by the computer processor of FIG. 1.

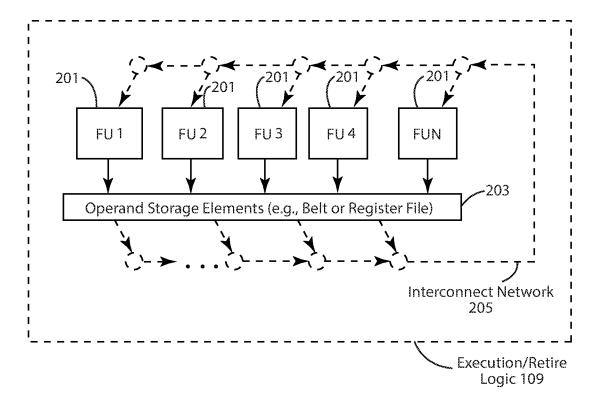

- FIG. 3 is schematic illustration of components that can be 60 part of the execution/retire logic of the computer processor of FIG. 1 according to an embodiment of the present disclosure.

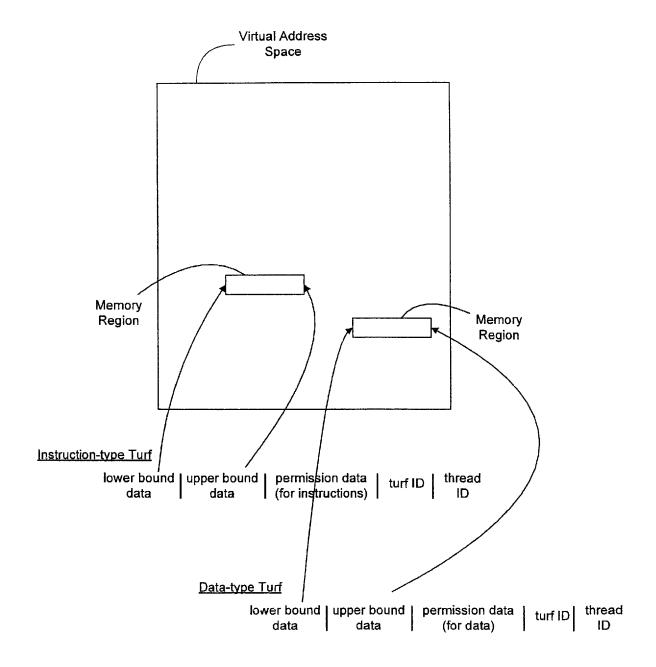

- FIG. 4 is schematic illustration of the instruction-type and data-type turfs that are used by the computer processor of 65 FIG. 1 to define and enforce protection domains for threads executing on the computer processor.

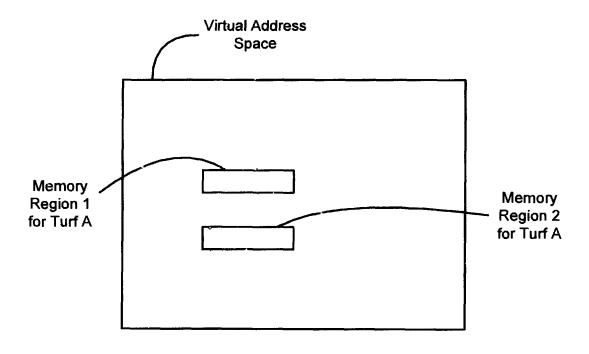

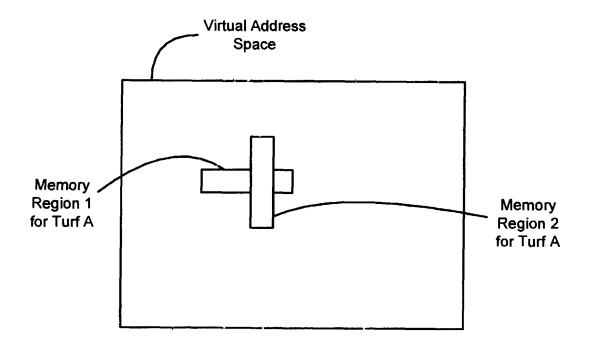

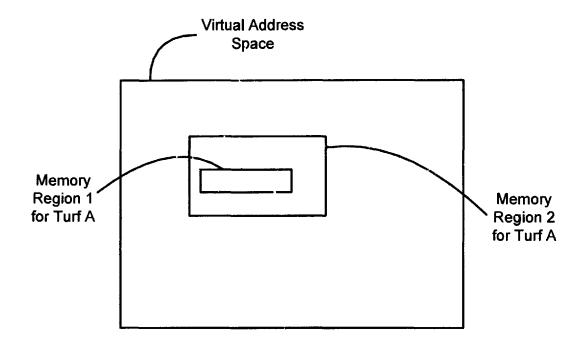

FIG. 5A is a schematic region of two disjoint memory regions specified by two instruction-type or data-type turfs.

FIG. 5B is a schematic region of two partially overlapping memory regions specified by two instruction-type or datatype turfs.

FIG. 5C is a schematic region of two overlapping memory regions specified by two instruction-type or data-type turfs.

FIG. 6A is schematic illustration of hardware registers storing turf-specific descriptors that are used by the computer processor of FIG. 1 to define and enforce protection domains for threads executing on the computer processor.

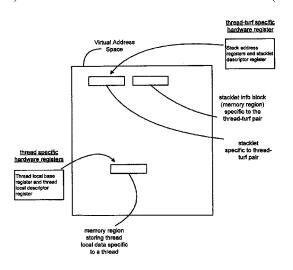

FIG. 6B is schematic illustration of hardware registers storing thread-turf-specific descriptors and thread-specific descriptors that are used by the computer processor of FIG. 1 to define and enforce protection domains for threads executing on the computer processor.

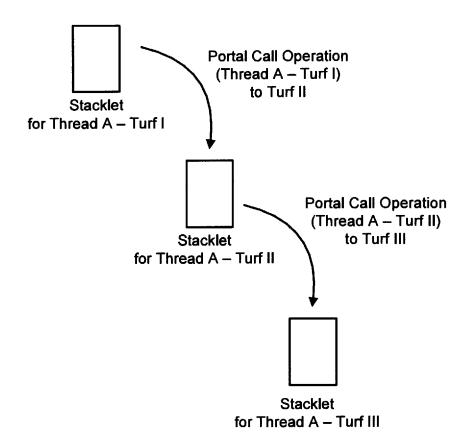

FIG. 6C is pictorial illustration of a logical call stack for a thread executing on the computer processor of FIG. 1.

FIG. 7 is a schematic block diagram of components that can be part of the execution/retire logic of the computer processor of FIG. 1 according to an embodiment of the present disclosure.

FIG. 8A is an illustration of the layout of a portal entry

FIG. 8B is an illustration of the information contained in a stacklet info block according to an embodiment of the present disclosure.

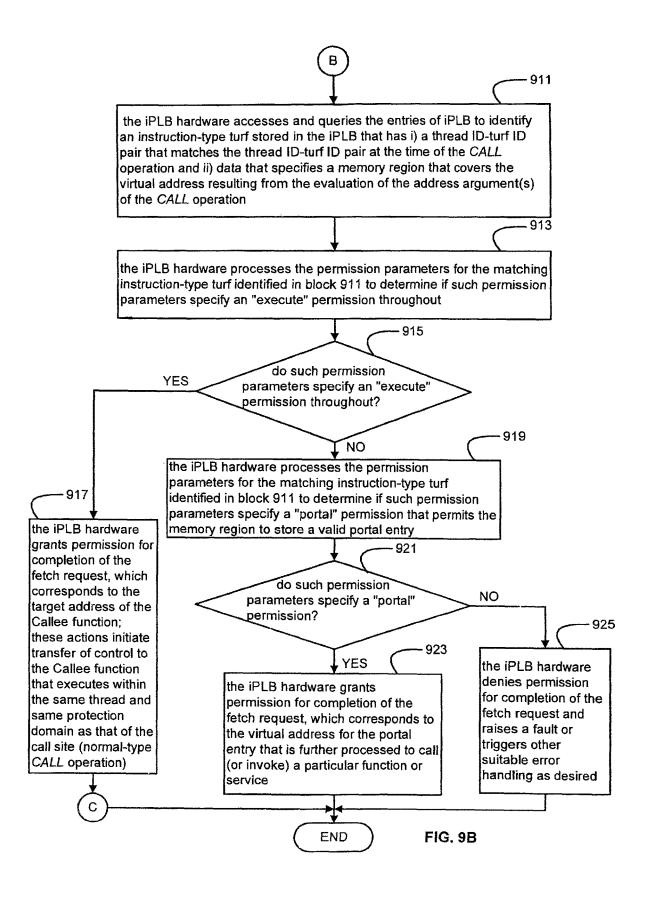

FIGS. 9A and 9B, collectively, is a flowchart illustrating the operations carried out by the computer processor in processing CALL operations, which includes normal-type CALL operations and portal-type CALL operations according to an embodiment of the present disclosure.

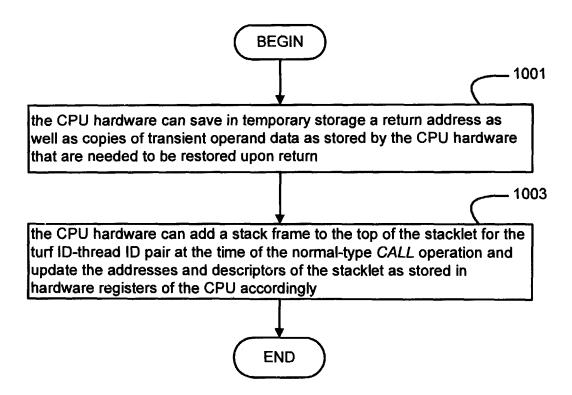

FIG. 10 is a flowchart illustrating actions carried out by the computer processor in processing a normal-type CALL

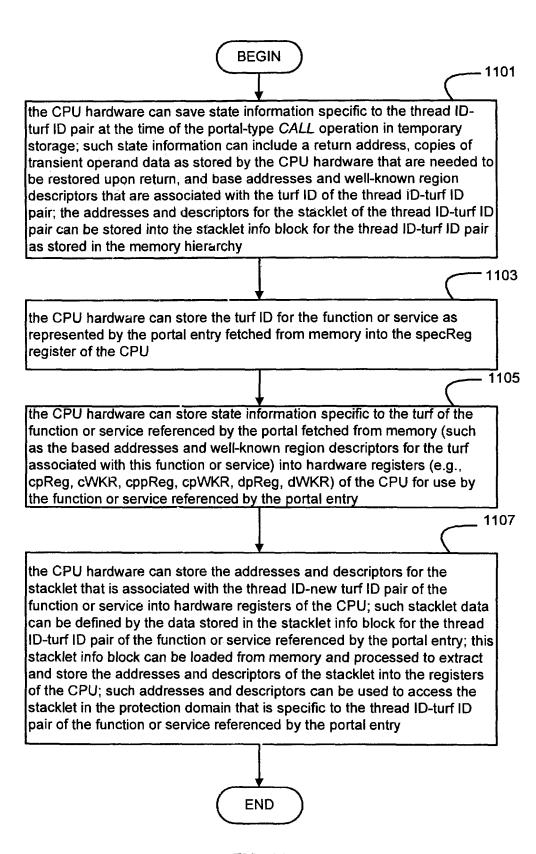

FIG. 11 is a flowchart illustrating actions carried out by the computer processor in processing a portal-type CALL operation.

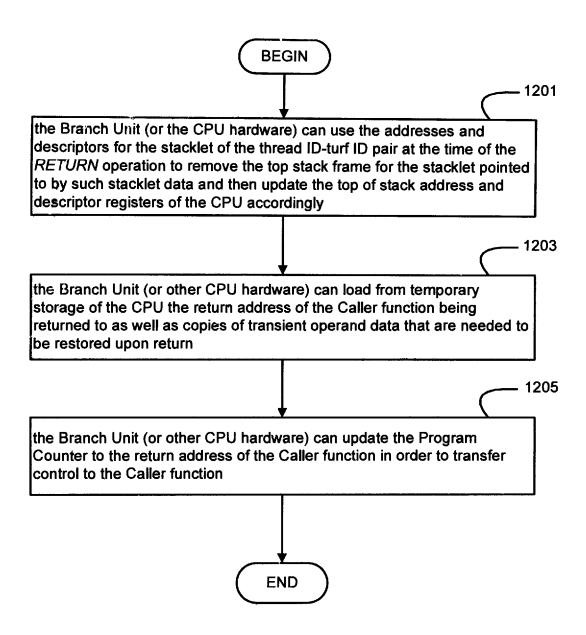

FIG. 12 is a flowchart illustrating actions carried out by the computer processor in processing a RETURN operation from a normal-type CALL operation.

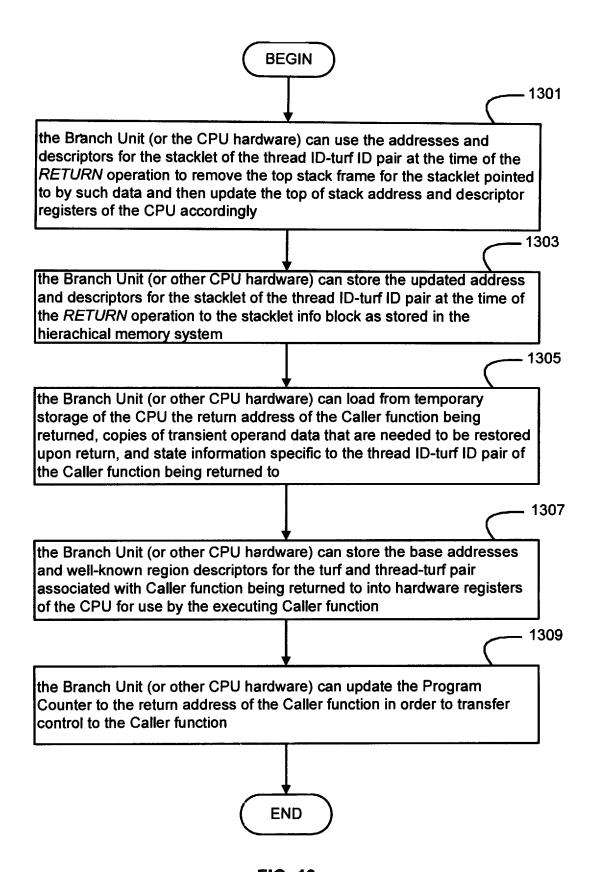

FIG. 13 is a flowchart illustrating actions carried out by the computer processor in processing a RETURN operation from a portal-type CALL operation.

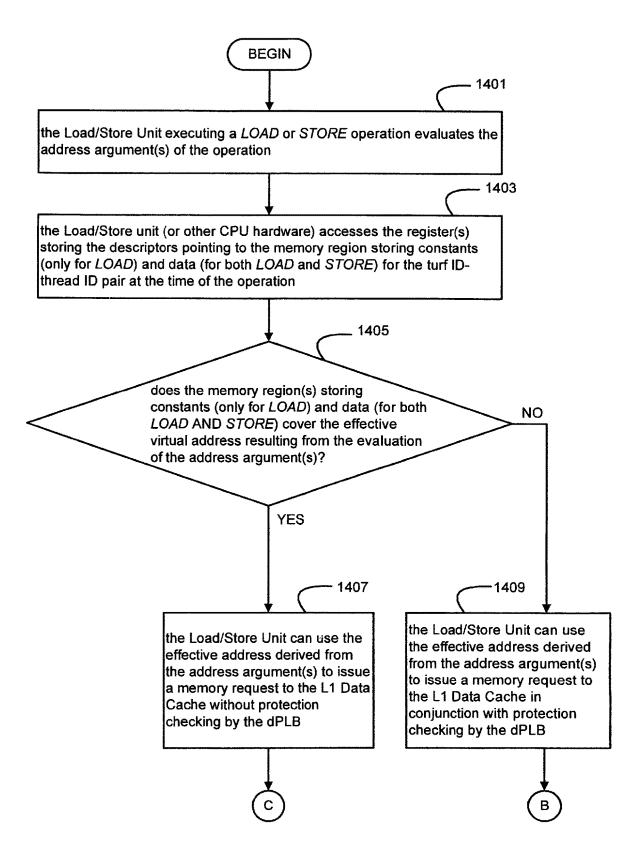

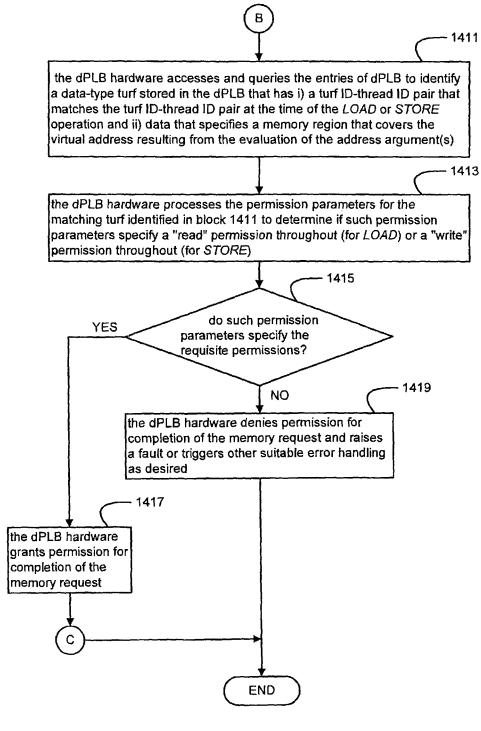

FIGS. 14A and 14B, collectively, is a flowchart illustrating the operations carried out by the computer processor in processing LOAD and STORE operations according to an embodiment of the present disclosure.

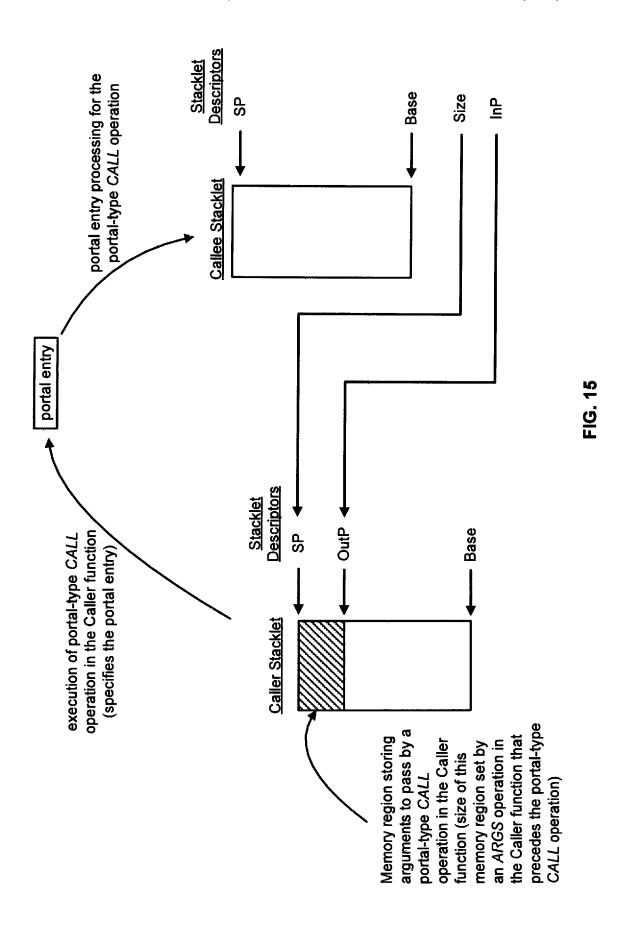

FIG. 15 is a schematic diagram of the processing of an ARGS operation and portal-type CALL operation that cooperate to pass one or more arguments stored in the stacklet of a Caller function to a Callee function according to an embodiment of the present disclosure.

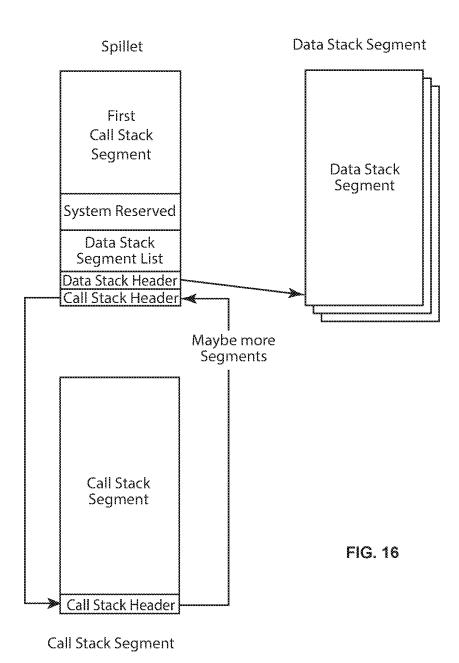

FIG. 16 is a schematic diagram of a spillet and corresponding data stack segment (or stacklet) and call stack

FIG. 17 is a schematic diagram of a global virtual address space using an example configuration.

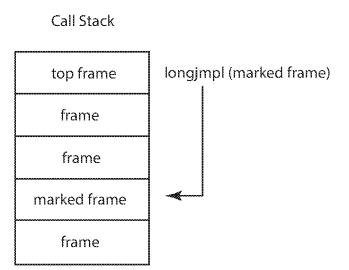

FIG. 18 is a schematic diagram of a call stack on which a longimpl operation is executed.

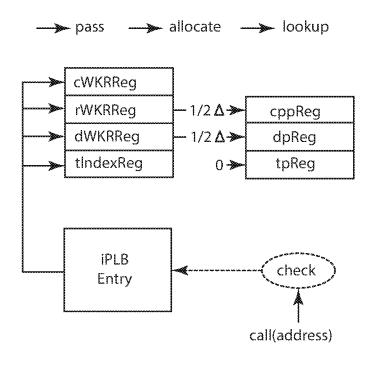

FIG. 19 shows operations that can be performed when a call address misses in the cWKR but hits in the iPLB or Permission Tables.

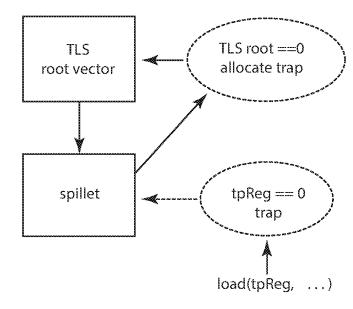

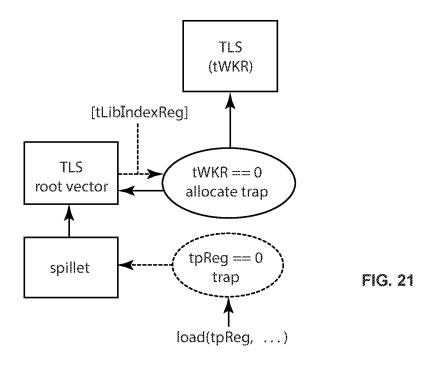

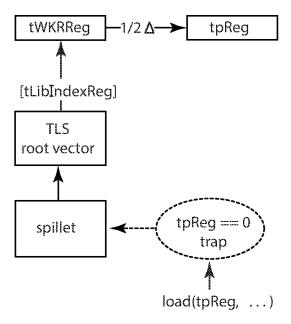

FIG. 20-22 shows operations that can be performed with respect to memory references based on the TLS base register, tpReg.

# DETAILED DESCRIPTION OF THE PREFERRED EMBODIMENTS

Illustrative embodiments of the disclosed subject matter of the application are described below. In the interest of clarity, not all features of an actual implementation are described in this specification. It will of course be appreciated that in the development of any such actual embodiment, numerous implementation-specific decisions must be made to achieve the developer's specific goals, such as compliance with system-related and business-related constraints, which will vary from one implementation to another. Moreover, it will be appreciated that such a development effort might be complex and time-consuming but would nevertheless be a routine undertaking for those of ordinary skill in the art having the benefit of this disclosure.

As used herein, the term "operation" is a unit of execution, such as an individual add, load, store or branch operation.

The term "instruction" is a unit of logical encoding including zero or more operations. For the case where an instruction includes multiple operations, the multiple operations are semantically performed together.

The term "hierarchical memory system" is a computer <sup>25</sup> memory system storing instructions and operand data for access by a processor in executing a program where the memory is organized in a hierarchical arrangement of levels of memory with increasing access latency from the top level of memory closest to the processor to the bottom level of <sup>30</sup> memory furthest away from the processor.

The term "cache line" or "cache block" is a unit of memory that is accessed by a computer processor. The cache line includes a number of bytes (typically 4 to 128 bytes).

The term "stack" is a region of memory associated with a thread that implements a function or subroutine. When the thread of the function or subroutine executes, it may add a stack frame to the top of the stack by the actions of an explicit or implicit CALL operation; when the function or subroutine exits by executing a RETURN operation, the top stack frame may be removed from the stack.

The term "stacklet" is one segment of a segmented data stack, and its contents are in general visible to load and store ops, at least up to the current top of stack. The stacklet stores 45 stack frames generated by execution of the particular thread executing in the particular turf.

The term "spillet" is one segment of a segmented call stack, which contains call linkages, save state, and transient grant tables. The spillet is generally not visible to load and 50 store operations but is instead manipulated by hardware or trusted system code.

The term "stack frame" is a frame of data pushed onto a stacklet by an executing thread. Each stack frame corresponds to an explicit or implicit CALL operation to a 55 function or subroutine whose execution as not yet terminated by a corresponding RETURN operation.

In accordance with the present disclosure, a sequence of instructions is stored in a hierarchical memory system and processed by a CPU (or Core) 102 as shown in the exemplary embodiment of FIG. 1. The CPU (or Core) 102 includes a number of instruction processing stages including at least one Instruction Fetch Unit (one shown as 103), at least one Instruction Buffer (one shown as 105), at least one Decode Stage (one shown as 107) and Execution Logic 109 65 that are arranged in a pipeline manner as shown. The CPU (or Core) 102 also includes Prediction Logic 111, at least one

8

Program Counter (one shown as 115), at least one L1 Instruction Cache (one shown as 117), and an L1 Data Cache 110

The L1 Instruction Cache 117 and the L1 Data Cache 119 are logically part of the hierarchical memory system. The memory system is organized as a single-address-space system where all program code and data reside and coexist in the same global virtual address space. The L1 Instruction Cache 117 is a cache memory that stores copies of instruction portions stored in the memory system in order to reduce the latency (i.e., the average time) for accessing the instruction portions stored in the memory system. In order to reduce such latency, the L1 Instruction Cache 117 can take advantage of two types of memory localities, including temporal locality (meaning that the same instruction will often be accessed again soon) and spatial locality (meaning that the next memory access for instructions is often very close to the last memory access or recent memory accesses for instructions). The L1 Instruction Cache 117 can be 20 organized as a set-associative cache structure, a fully associative cache structure, or a direct mapped cache structure as is well known in the art. Similarly, the L1 Data Cache 119 is a cache memory that stores copies of operands stored in the memory system in order to reduce the latency (i.e., the average time) for accessing the operands stored in the memory system 101. In order to reduce such latency, the L1 Data Cache 119 can take advantage of two types of memory localities, including temporal locality (meaning that the same operand will often be accessed again soon) and spatial locality (meaning that the next memory access for operands is often very close to the last memory access or recent memory accesses for operands). The L1 Data Cache 119 can be organized as a set-associative cache structure, a fully associative cache structure, or a direct mapped cache structure as is well known in the art.

The hierarchical memory system of the CPU/Core 102 can also include an L2 instruction/data cache 121 as well as main memory 123 as shown in FIG. 1. The caches 117, 119, 121 store tags defined by virtual addresses and thus are virtual caches. The protection model of the system can be enforced by two protection lookaside buffers, one labeled iPLB that can be viewed as part of the L1 Instruction Cache 117 and one labeled dPLB that can be viewed as part of the L1 Data Cache 119. Specifically, the protection lookaside buffer iPLB provides for access control of instructions, restricting the kinds of access and the addresses for instructions that are accessible to the program. The protection lookaside buffer dPLB provides for access control of operand data, restricting the kinds of access and the addresses for operand data that are accessible to the program. Such access control is enforced before program accesses to the corresponding cache are allowed to complete. However, the cache access may be carried out in parallel with the protection checking, which removes protection from the program critical path. A memory controller 125 provides an interface between cache and external main memory 123. The memory controller 125 supports virtual memory with paging where the global virtual address space of the memory system is divided into equal chunks of consecutive memory locations called pages. Pages are dynamically mapped to pages of the physical address space of the main memory 123 through a set of translation tables called page tables. In order to speed up virtual address translation, the memory controller 123 stores current address translations in a separate cache called the translation lookaside buffer (TLB). As noted above, a separate virtual address space or memory access hardware may exist for instructions and data. In this case, the memory

controller 123 can include distinct TLBs for each access type, an Instruction Translation Lookaside Buffer (iTLB) and a Data Translation Lookaside Buffer (dTLB). Note that because the cache of the memory hierarchy are virtual caches, the protection function provided by the PLB(s) that 5 are part of the top level cache is split from the virtual-tophysical address mapping function provided by the TLB(s) of the memory controller 123.

In other implementations, a single virtual address space or memory access hardware may exist for instructions and data. In this case, the top level of cache can include a single PLB, and the memory controller 123 can include a single TLB to handle both instructions and data. Other memory hierarchy organizations can also be used.

The Program Counter 115 stores the memory address for a particular instruction and thus indicates where the instruction processing stages are in processing the sequence of instructions. This memory address can be derived from a predicted (or resolved) target address of a control-flow 20 operation (branch or call operation), the saved address in the case of a return operation, or the sum of memory address of the previous instruction and the length of previous instruction. The memory address stored in the Program Counter 115 can be logically partitioned into a number of high-order 25 bits representing a cache line address (\$ Cache Line) and a number of low-order bits representing a byte offset within the cache line for the instruction.

The Prediction Logic 111 employs a mechanism to predict the logical chain of instruction portions (e.g., cache lines) that is to be executed by the CPU 102. The prediction of the chain of instruction portions can be generated and stored ahead of the Decode Stage 107. The operation of the Prediction Logic 111 can be used to control prefetch operations that prefetch the cache lines that make up the logical 35 chain of instruction portions. The operation of the Prediction Logic 111 can be used to control fetch operations carried out by the Instruction Fetch Unit 103 that fetch such cache lines from the L1 Instruction Cache 117 into the Instruction Buffer to control read-out operations that read-out the sequence of instructions within the logical chain of instruction portions from the Instruction Buffer 105 to the Decode Stage 107 as well as to control shifting operations that operate on cache lines to isolate each instruction for decoding and follow-on 45 execution. During start-up and mispredict recovery, the logical chain of instruction portions begins at the target memory address stored by the Program Counter 115.

The Instruction Fetch Unit 103, when activated, sends a memory request to the L1 Instruction Cache 117 to fetch a 50 cache line from the L1 Instruction Cache 117 at a specified cache line address (\$ Cache Line). This cache line address can be derived from the operation of the Prediction Logic 111. The L1 Instruction Cache 117 services this request (possibly accessing lower levels of the hierarchical memory 55 system if missed in the L1 Instruction Cache 117), and supplies the requested cache line to the Instruction Fetch Unit 103. The Instruction Fetch Unit 103 passes the cache line returned from the L1 Instruction Cache 117 to the Instruction Buffer 105 for storage therein.

The Decode Stage 107 is configured to decode one or more instructions stored in the Instruction Buffer 105. Such decoding generally involves parsing and decoding the bits of the instruction to determine the type of operation(s) encoded by the instruction and generate control signals required for 65 execution of the operation(s) encoded by the instruction by the Execution/Retire Logic 109.

10

The Execution/Retire Logic 109 utilizes the results of the Decode Stage 107 to execute the operation(s) encoded by the instructions. The Execution/Retire Logic 109 can send a load-type memory request to the L1 Data Cache 119 to load data from the L1 Data Cache 119 at a specified memory address. The L1 Data Cache 119 services this load-type memory request (possibly accessing the lower levels of the hierarchical memory system if missed in the L1 Data Cache 119), and supplies the requested data to the Execution/Retire Logic 109. The Execution/Retire Logic 109 can also send a store-type memory request to the L1 Data Cache 119 to store data into the memory system at a specified address. The L1 Data Cache 119 services this store-type memory request by storing such data at the specified address (which possibly involves overwriting data stored by the L1 Data Cache 119 and lowering the stored data to lower levels of the hierarchical memory system).

The instruction processing stages of the CPU (or Core) 102 can achieve high performance by processing each instruction and its associated operation(s) as a sequence of stages each being executable in parallel with the other stages. Such a technique is called "pipelining." An instruction and its associated operation(s) can be processed in five stages, namely, fetch, decode, issue, execute and retire as shown in FIG. 2.

In the fetch stage, the Instruction Fetch Unit 03 sends a request to the L1 Instruction Cache 117 to fetch a cache line from the L1 Instruction Cache 117 at a specified cache line address (\$ Cache Line). The Instruction Fetch Unit 103 passes the cache line returned from the L1 Instruction Cache 117 to the Instruction Buffer 105 for storage therein.

In the decode stage, one or more instructions stored in the Instruction Buffer 105 are decoded by the Decode Stage 107. Such decoding generally involves parsing and decoding the bits of the instruction to determine the type of operation(s) encoded by the instruction and generating control signals required for execution of the operation(s) encoded by the instruction by the Execution/Retire Logic 109.

In the issue stage, one or more operations as decoded by 105. The operation of the Prediction Logic 111 can be used 40 the Decode Stage 107 are issued to the Execution/Retire Logic 109 and begin execution.

In the execute stage, issued operations are executed by the functional units of the Execution/Retire Logic 109 of the CPU/Core 102.

In the retire stage, the results of one or more operations produced by the Execution/Retire Logic 109 are stored by the CPU/Core 102 as transient result operands for use by one or more other operations in subsequent issue/execute cycles.

The Execution/Retire Logic 109 includes a number of functional units (FUs) which perform primitive steps such as adding two numbers, moving data from the CPU proper to and from locations outside the CPU such as the memory hierarchy, and holding operands for later use, all as are well known in the art. Also within the execution/retire logic 109 is a connection fabric or interconnect network connected to the FUs so that data produced by a producer (source) FU can be passed to a consumer (sink) FU for further storage or operations. The FUs and the interconnect network of the Execution/Retire logic 109 are controlled by the executing program to accomplish the program aims.

During the execution of an operation by the Execution/ Retire Logic 109 in the execution stage, the functional units can access and/or consume transient operands that have been stored by the retire stage of the CPU/Core 102. Note that some operations take longer to finish execution than others. The duration of execution, in machine cycles, is the execution latency of an operation. Thus, the retire stage of an

operation can be latency cycles after the issue stage of the operation. Note that operations that have issued but not yet completed execution and retired are "in-flight." Occasionally, the CPU/Core 102 can stall for a few cycles. Nothing issues or retires during a stall and in-flight operations remain 5 in-flight.

11

FIG. 3 is a schematic diagram illustrating the architecture of an illustrative embodiment of the Execution/Retire logic 109 of the CPU/Core 102 of FIG. 1 according to the present disclosure, including a number of functional units 201. The 10 execution/retire logic 109 also includes a set of operand storage elements 203 that are operably coupled to the functional units 201 of the execution/retire logic 109 and configured to store transient operands that are produced and referenced by the functional units of the execution/retire 15 logic 109. An interconnect network 205 provides a physical data path from the operand storage elements 203 to the functional units that can possibly consume the operand stored in the operand storage elements. The interconnect network 205 can also provide the functionality of a bypass 20 routing circuit (directly from a producer functional unit to a consumer function unit).

The protection model of the CPU dictates which parts of the virtual address space of the memory system can and cannot be accessed by different parts of program code 25 dynamically as the program code executes on the CPU. The protection model employs permissions that are tied to virtual addresses, or rather address ranges. There are no privileged operation modes or restricted instructions. All access questions are dealt with via access to virtual addresses. An 30 address range is just a start address and an end address, and a permission attached to a range applies to start and end address and everything in between. As for the permissions themselves, the protection model of the CPU supports the classic read and write permissions, as well as the execute 35 permission that has become more and more prevalent in mainstream architectures in recent years. There are more kinds of permissions, of which the portal permission is particularly important, since it enables the transition between different protection domains. But there is also a 40 grant permission, a session permission and possibly more.

The short forms of these permissions are r, w, x, p, g, s. r or Read permissions are checked on load operations. w or Write permissions are checked on store operations.

- x or Execute permissions are checked on every instruction 45 load initiated by the CPU, whether from normal sequential execution or from execution transfer operations like branch operations, call operations, and return operations.

- p or Portal permissions are checked only on call opera- 50 tions.

- g or Grant permissions are checked on persist operations. s or Session permissions are checked on session operations.

Checking permissions in this context means checking 55 whether the current protection domain has the required permission flags set for the required address within one of the ranges in this protection domain. That's what a protection domain is in general: a collection of permissions for different resources. Since all permissions are tied to address 60 ranges, a protection domain or turf is an identifier with a collection of address ranges with permissions attached to it. Permissions are attached to a protection domain (turf) by the grant operation, which has three basis components:

- 1. an address range

- 2. different permission flags

- 3. the protection domain (turf) this applies to

These three components don't necessarily need to be explicitly stored together in one data structure. In different hardware contexts either one or both, the permission flags and the protection domain, are often implicitly defined by the memory location or register an address range is stored in. Also note that some grant operations include additional data

fields as described herein.

12

The granting and revoking of permissions by program code segments (threads) can be regulated by the permissions that the thread already has. For example, if a thread has read or write permissions to an address range, the thread can pass on the read or write permissions respectively on this range to another thread or can choose to pass on the read or write permission for a part (subrange) on this range. With this context, an initial all-grant provided by the hardware at power-up can be broken down hierarchically into ever smaller grants via delegation. The all-grant is a special permission setup on boot. It covers the whole address space and gives read and write permissions to the initial turf. The grant and session permissions only become applicable when two threads exist and communicate with each other. The initial boot code must have execute permissions too, and for this reason an initial execute grant exists in addition to the all-grant.

The CPU can support two different kinds of grant operations, transient grants and persistent grants. Transient grants are temporary, and are created for the purpose of a single transaction between two different protection domains, between two different turfs. Immediately after the transaction for which they were created completes, the transient permissions are revoked again, automatically, when the stack frame that they are granted for is exited. Persistent grants are attached to turfs, and once they are granted they tend to persist for the remainder of the life time of the turf. Some tasks, like the unloading of libraries, can of course remove persistent permissions again, but it is a comparatively rare occurrence, and it has to be done explicitly. Persistent grants can only be created by either directly accessing the permission data structures in privileged applications, or by creating them from a transient grant via a handshake. Transient grants, and only transient grants, can have the grant permission in addition to other flags. A grantee of such a transient grant can create persistent permissions from the transient permission for its own turf, or on a subrange or a subset of the rights. The grant right itself of course cannot be passed on. It is possible without further restriction to create new transient grants from the persistent grants that a thread has, or to pass on transient grants to other threads.

In the single-address-space system of the memory system, all program code (applications) resides and coexists in the same global virtual address space. It is still a virtual address space, in that it maps the all possible addresses used by the program code to available physical memory. Addresses can be freely shared between different program code, requiring no expensive remapping. And while there is still a single virtual address space to map to physical memory, shared by all program code, this has no protection domain semantics. Furthermore, memory address translation (from the virtual address space to the physical memory address space) is about resource utilization, and doesn't need to happen on every memory access. Specifically, such memory address translation is only needed when loads miss in cache or cache lines are evicted and there is actual access to physical 65 memory. This represents a decoupling of access checks and memory address translation. Such decoupling allows for the permissions/turfs as explained above to be applied at byte

granularity (where the address range(s) of the turfs have byte granularity), while memory address translation is carried out at the physical page granularity. Furthermore, the access checking can be carried out in a far bigger extent than pages, before any translation takes place.

A turf is uniquely identified by a key, the turfID. In one embodiment, the size of the turfID can be configurable to be in the range of 20 to 32 bits. Address range permissions (also referred to herein as region descriptors and associated permissions) are attached to the turfID, and thus it serves to 10 identify as a protection domain. Note that such a protection domain provides for protection without isolating applications into different address spaces. Thus, read only data and code can be shared between different program code in the single-address-space system and all program code uses the 15 same addresses to access them. This is in contrast to multiple address space systems, where most code and read only data must go through an expensive relocation step to fit them into the application address space.

In addition to assigning grants to turfs with the turfID, the 20 turfID can be used to efficiently perform simple address mappings to support the copying of address ranges without invalidating pointers in those address ranges. This is necessary to implement fork() in a single address space system. The single global address space can be accessed as many 25 different local spaces. To implement this distinction, addresses can be absolute global addresses where the same bit pattern always points to the same location in the single global address space for every turf. Or they can be local addresses, where the same bit pattern points to the same 30 relative location within the mapping of a turf. These different kinds of addresses form one global and many local address spaces. These local spaces are not fully fledged virtual address spaces like in a multiple address space system. They are rather a simple mapping on top of the 35 single global virtual address space. All grants are defined in the global address space, and permissions are checked using global addresses. The main reason local and global addresses exist, as mentioned, is to make forking possible, to easily be able to copy the memory from a local address 40 space into a different location in the global address space as a different local space, and still have contained pointers point to the same relative locations within the new local space. And as long as the program code only uses local pointers, this is possible.

Global and local addresses can be distinguished by the highest order bit 63 (or L bit) in a 64-bit virtual memory address as shown in Table A below:

size can be a multiple of the page size. The turfIDMask is obtained by shifting the turfID left to reflect the minimum plot size. That is, turfIDs can be seen as being indexes into an array of plots in memory, and the turfIDMask is the byte address of the particular indexed plot. When the highest order bit is zero, nothing else needs to be done. In this case, the bit pattern is the global address. When it is one, the turfIDMask needs to be applied. An example using C operators follow:

14

turfID=0x12345678, leftShift=20 turfIDMask=0x12345678<<20|1<<63= 0x8001234567800000 globalAddress=0x0123456701234567 localAddress=0x0123456701234567 ^0x8001234567800000=0x8122662266A34567 0x8122662266^0x8001234567800000= 0x0123456701234567=globalAddress

A consequence of this is that local address spaces consist of power of two-sized plots and the lowest set bit of the turfID determines the maximum plot size of the local address space of a turf, i.e. all the bits lower than the lowest set bit of the mask comprise the offset into the plot segment. The number of bits in the turfID and the left shift define the minimum and maximum plot size are a member dependent machine configuration. Note that one distinguished plot, called the home plot of the turf, has local address zero, and necessarily the global address equal to the turfIDMask. A turf doesn't even have to use any local addresses at all, but as long as a turf needs to be able to be forked, it will have to.

Note that all addresses in the virtual address space can point to the same location for all turfs and the local address space each of them defines. This does not mean a turf gets to allocate or reserve all of the addresses of the virtual address space (e.g., 64 ZB of a 60 bit address space). Instead, the virtual address space must be reserved and allocated before it can be used. Specifically, the global space and all local spaces are divided up by the hardware and the OS and appointed to use for different turfs according to all kinds of criteria. This is reservation, but reserved address space is still not accessible by the turf, for that there must exist permission for them to actually use it. Only with permissions does the address space become usable for the turf and is allocated. And even allocated memory doesn't initially take any space in the caches or physical memory due to backless memory mechanisms as described in U.S. patent application Ser. No. 15/515,058, filed on Oct. 15, 2014, commonly assigned to the assignee of the present application and herein incorporated by reference in its entirety.

### TABLE A

| L | Res | Address                                 |

|---|-----|-----------------------------------------|

| x | xxx | xxxxxxxxxxxxxxxxxxxxxxxxxxxxxxxxxxxxxxx |

When the L-bit is set, it is a local address and the global address can be derived by the XOR of the local address and a base address derived from the turfID, called turfIDMask, as follows:

Global Address=Local Address XOR turfIDMask When the L-bit is cleared, it is a global address and the local address can be derived by the XOR of the global address and the turfIDMask as follows:

Local Address=Global Address XOR turfIDMask

This arrangement segments to local address spaces in 65 power of two sized chunks of consecutively addressable memory. These segments are called plots. The minimum plot

Due to the way local addresses are constructed from global addresses, by XORing with a left shifted turfID, local spaces have several interesting properties as follows:

The turfID bitmask implicitly defines a home plot in the global address space for every possible turf. This home plot resides in the global address space where the local address, consisting of the global address XORed with turfIDMask, would be zero. One implication of this is: turfs with smaller maximum plot sizes are more numerous than turfs with larger maximal plot sizes

There is one turf, with a turf ID all zero but the highest ID bit, which has the largest regular plot size

55

60

there is one turf, with a turf ID of zero, whose plot size is all of memory and whose home plot is located at global address zero.

turfs with larger home plots overlay spaces that could have been used for multiple turfs with smaller plot sizes 5 home plots must reside in a dedicated section the global address space

The minimum and maximum plot size, and with it the number of available turfIDs, can be tuned to fit the work profiles and resource requirements of specific processors, 10 which results in different bitmask lengths of the turfID, which should generally be between 20 and 32 bits.

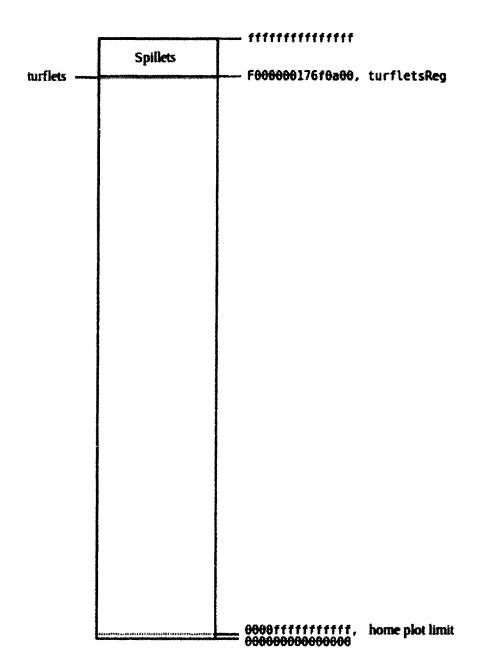

There can be quite a bit of administrative data associated with turfs, and the CPU hardware must be able to find this data quickly without having to consult software. For this 15 reason, the CPU hardware can maintain a turflet array. The turflet array can be located at a predefined address in the global address space. This predefined address can be read from the turfletsReg special register. The turflets array has as many entries as there are possible turfIDs, and each entry 20 has a predefined power of two size. The entries of the turflet array (turflets) correspond to the different turfs and can contain pointers to event handlers, permission search trees, resource limits and other things. Zero can be a meaningful default for the data contained in the turflet array. In one 25 embodiment, a turf almost never has read or write access to its corresponding turflet or any other turflet corresponding to other turfs.

A turf is set of address range permissions attached to a turfID. While turfs isolate the permission sets on memory 30 regions, threads isolate the control flow of program code working with those memory regions. In other words, a thread is a contained flow of execution. A turf can be associated with a particular thread during execution of the thread. In this sense, the particular thread executes within 35 the turf and the address range permissions that belong to the turf are used during execution of the particular thread to dictate which parts of the virtual address space of the memory system can and cannot be accessed by the execution of the particular thread. Like a turf, each thread is identifi- 40 able by a unique key referred to as a threadID. Unlike turfs, there are no additional semantics attached to the threadIDs. In one embodiment, the size of the threadID can be configurable to be in the range of 20 to 32 bits. The threadID of the currently executing thread can be kept in threadReg 45 special register. The turfID of the turf associated with the currently executing thread can be kept in the turfReg special register. When the threadReg register is set to X and the turfReg register is set to Y, it is said that thread X is (running) in turf Y. When thread X isn't currently executing, 50 it is said thread X is parked in turf Y, where turf Y will be the current turf for thread X if it is reactivated.

In one embodiment, a new thread can be created with a dedicated spawn operation as follows:

threadID spawn(void\* target, args argv)

The target argument is a code address to start execution at. The args and argv arguments are function arguments as for any normal function call. The spawn operation returns a threadID for the newly created thread. The spawn operation allocates a new hardware threadID and sets up the hardware 60 data structures to manage the newly created threads, called a spillet. The new thread is parked in the current turf to execute at the given target address with the given arguments in the new thread context later. The arguments are passed using the same mechanism calls use to pass arguments. It 65 returns the newly created threadID. How exactly hardware threadID generation is implemented can vary. It can be

16

incrementing counters with reuse buffers, it can be fully randomized, it even can be implemented as an abstract operation, i.e. as a function. Since there are no restricted operations, runaway thread creation could be a problem. Fortunately, this can be caught by the memory allocation interrupts when spillets are evicted from the caches.

For transferring control to a thread without creating a new one there is the dispatch operation:

void dispatch(threadID next)

The dispatch operation takes one argument, the threadID to next transfer to. It will park the current thread in the current turf and transfer control to the next thread, starting it for the first time or restarting it. In parking the current thread, the thread context of the current thread can be saved in a special hardware managed memory region. The data that comprises a thread context can vary by design. In one embodiment, it can contain the contents of the operand storage (e.g., belt, scratchpad), all task saved special registers like the stack pointer, the code pointers etc. The operation can raise a fault if the next thread is not parked in the same turf as the current thread.

The hardware resources used for threads (including special memory regions and threadIDs) can be reclaimed by the following operations:

void suicide(threadID next)

bool fratricide(threadID id)

The suicide operation essentially works like dispatch, but instead of saving the current thread state, it clears it and reclaims everything. The fratricide operation only works in threads currently parked in the same turf. It simply reclaims all hardware resources allocated for the thread. It will do nothing and return false if the thread is currently running, as recognized by the flag set by dispatch.

Note that whenever any of the above operations with a next ThreadID parameter fault, the fault handler must schedule a new thread. If the application handler does not resolve the fault, the fault cascades to the system fault handlers, which ultimately will result in a thread chosen by the operating system if no earlier fault handler catches it.

The CPU can maintain separate data and call stacks. This separation makes physically impossible most of the common stack overflow exploits that are so prevalent on current hardware, because the call stack, and the return and other pointers in it are not available to application code. Both data and call stacks are bound to threads and turfs and are segmented, so they can grow practically without limit. The CPU can also employ a dedicated hardware module referred to as the spiller that operates at the center of stack management. The spiller can manage the call stacks directly, from dedicated memory regions, which are never directly accessible by the application that uses them.

In one embodiment, the spiller employs a dedicated memory region referred to as the spillet array for managing the calls stacks. Like the turflets array, the spillet array is an array in global address space with easily computed entry addresses. The spillet array is two dimensional and the dimensions are the threadID and turfID. The entries of the spillet array, which are referred to herein as spillets, each have a convenient power of two size, and compared to turflets is larger (for example, a whole 4 kB page or even more). A spillet and corresponding data stack segment (or stacklet) and call stack segment are shown in FIG. 16. The internal organization of the spillet can be varied by design, but it contains the stack headers for both the call and data stacks, handles for transient permissions, and the data to park and resume threads. It can also contain reserved space for operating system defined use. The spillet can also store

the first call stack segment, making it unnecessary to allocate memory via software for portal call or thread transitions. This feature can reduce the time for thread and portal call switches. More call stack segments can be added, each containing a call stack segment header, like the spillet array 5 entry itself, but not all the other data. These call stack segments form a linked ring list with the headers containing the pointers. The header pointing to the currently in use call stack segment is always written in the spillet, so the hardware always knows where to find the current call stack top. Like for the turf headers, a fully zeroed entry is a meaningful initialization, in this case indicating an unused spillet array entry. Note that while the space for spillets is reserved in the address space, there is no associated physical space or DRAM for unused spillets. Thus only the spillets actually in 15 use by some thread running in some turf ever occupy memory. While the amount of the virtual address space reserved for spillets is large, it is dwarfed by the size of the overall 60-bit virtual space. The base of the spillet array is also a predefined address. For example, it can be the same 20 address from the turfletsReg register where the turflet array extends downward and the spillet array extends upward.

In contrast to the call stacks, the data stacks often, but not always, have to be fully accessible to the application turf. At least the current data stack frame must be accessible to the 25 running application. The operand storage (e.g., belt and scratchpad) of the CPU can reduce the need for actual data stack severely and often it is not needed at all. For this reason, data stack segments are only allocated when they are really needed, when the stackf() operation is called for the 30 first time in a thread in a turf. This triggers a stack overflow trap, and the handler allocates the data stacks according to the application needs, with the growth behavior it needs. The data stack header has a header that holds the administration data for the data stack such as the stack pointer and frame 35 pointer into the current segment. The header is stored at a defined location in the corresponding spillet array entry for fast access. Additionally, because unlike for the call stack the segment headers can't be stored in the segment itself here, there is a sorted array to the potentially many data stack 40 segments. These segments are allocated at size alignment, and don't need to be all the same size, the stack allocation handler can implement any sizing strategy.

FIG. 17 shows the global address space using an example configuration with 24 bit turfIDs, 20 bit threadIDs, 1 MB 45 minimum plot size, and additionally 4 kB turflet and spillet size.

Since the control stacks are hidden from application access and are fully managed by hardware, any control scheme that is commonly implemented by explicit stack 50 manipulation can be implemented as machine operations on the CPU. One such control scheme is the long jump pattern well known from the C standard library. The operations are: handle setjmpl()

op longjmpl(handle target, op value)

These very much resemble the C functions. Handle is an opaque 8-byte structure that identifies the saved stack and execution state internally for the spiller. longjmpl has a return value because it needs to make it available on the belt for the code to continue. It can of course only be called from places that are down the call stack from where the setjmpl has been called, and it will fault if the handle is illegal. It will also fault if the handle was created in a different turf. The mechanisms employed to implement these operations can be the same that are implemented to facilitate normal calls and 65 returns and dispatch. More specifically, the setjmpl operation creates exactly the same data structures in the call stack

in spiller space that the dispatch operation would create, or a call would create to save the caller frame. It saves the current frame, creates a new frame by copying the current one. And then it drops the current frame index of the current stack as a handle into the new frame and transfers control there. The spiller also saves the state of the operand storage (e.g., belt), the instruction pointers and all other call saved special registers. Note that the turf and thread are implicit from the spillet address. Each call frame has a very regular defined layout and size as it is completely hardware managed. The longjmpl operation implements what would be the second part of the dispatch or the return operation, reinstating the execution context from the call stack, acting as a kind of multi-level return. FIG. 18 shows a continuous logical view, i.e. without taking stack segments into account, of a call stack on which a longjmpl operation is executed.

A single thread can be active in different turfs, at different times, depending on the requirements of the application and the protection requirements of the different components. Portals allows for threads to cross turf boundaries. Portals bring threads and turfs together in the conceptual, but also the very literal way: A portal is a data structure that consists of:

target memory address to transfer thread control next to a portal permission on the location the target memory address is stored in memory, the permission with a TurfID for the new context of the thread

In memory a portal is just a pointer to an entry point. It can be a single pointer with a single portal grant on that one pointer address. It can also be a whole array of entry points with a portal grant spanning all of it. Such a portal array can be the definition of the full API of a service library. Such services, in isolated turfs, potentially with privileges on important address ranges, but without needing a primary thread, can be an important security feature. Active applications with running threads can call into services though published portals and have tasks performed for them safely and with minimal overhead. The most prominent example of a service would be a kernel that implements system calls through portals.

Portals are invoked with a normal call operation to the portal's address and are referred to as portal-type call operations herein. The portal-type call operation includes the following steps:

- The memory access check on the called address reveals a portal permission.

- The TurfID is retrieved from the permission and placed into turfReg.

- 3. The target memory address is retrieved from the called location.

- A memory access check is performed on this target memory address for x or p

- 5. If target address has an execute permission, control is transferred there with the passed arguments (for example on a new belt) of the new frame.

- If it has a portal permission again, the steps 2-5 are repeated, but only once.

Often the caller of the portal doesn't even need to be aware it is a portal. It calls the address the portal is stored in like any other address. Applications control the creation of portals into their turf, but if everyone could pass through, there wouldn't be much safety involved in portals. This is why the portal permission exists. The addition of step six, the potential one time repeat of the portal call steps, serves as a means to allow multiple services to be presented as one defined API to applications and to possibly swap them out at runtime even without the applications being aware. The limit

of one step prevents circular portal structures and a neverending attempt by the hardware to find actual code. If a location with execute permission is not found by the second iteration, then the caller is faulted with invalidAddressFault.

A transient grant operation is tied to a particular portal-type call operation. While communicating through a portal-type call operation is a function call in the hardware implementation, semantically it is a transaction: a single exchange of information between two isolated and possibly distrustful parties. In general, the caller is the client and the callee is the server, and the set of calls offered by the server to clients is a service. In an ordinary function call, the caller may pass arguments to the callee, and the callee may return results, but in addition caller and callee share much other state: global data, heap contents, and even data internal to other functions lower in the stack. Both caller and callee accept this arrangement because they trust each other; the call is a convenient and clean way to cause an action to be performed, but has no protection or security aspect.

A portal-type call operation can provide the convenience 20 of a call-like interchange between client and server, except that the parties share only the arguments and results of the call. The arguments and results form the entirety of the interchange; neither party can see or modify any other state of the other. This isolation is typical of inter-process com- 25 munication (IPC) of other systems. IPC does provide isolation, typically using the page mapping hardware for the purpose, but it usually is large-granularity, inconvenient, and slow. While conventional IPC is possible on the CPU, the CPU can provide portal-type call operations as a much 30 lighter weight alternative. In conventional IPC each party is a process, a notion that combines a protection domain, some data reachable from that domain, and one or more threads of control, all wrapped up together. On the CPU, these notions are distinct: the protection domain is a turf, which may or 35 may not have either data or threads associated with it. With IPC a client thread physically passes argument data (usually pages) to a server process, where a server thread then uses the data arguments and the data of its own process to produce some result, which is then sent back to the client. 40 Finally, a client thread examines the results and continues execution. In contrast, on the CPU, when a client thread calls a portal via a portal-type call operation, the protection domain that the thread is running in changes from that of the client turf to that of the server turf. In effect, the former client 45 thread becomes a server thread, temporarily, and remains one until it returns from the call. At that point, it doffs the server disguise, reenters the client turf, and becomes again a client thread. However, in its brief incarnation as a server thread, it had full access to the server data and state, because 50 it was, as a server thread, running in the server turf. In addition, it had access to the arguments to the call, and was able to use those arguments and the server state to perform the service requested by the call. While a server thread, it has no access to any client state except the arguments. The 55 temporary server thread will return from the portal-type call operation after producing the desired results. The return carries the results back, but no other server state, and the thread, now properly a client thread, can continue executing with those results.

A portal-type call operation can carry arguments and returns results, and in machine terms it uses much the same calling convention that is used for normal calls. As on many machines, the CPU can possibly use several different mechanisms for passing arguments and results (such as passing on 65 operand storage such as the belt, in registers, in memory, and by reference.

20

When passing arguments on the belt or in registers, the arguments of the portal-type call operation have exactly the same meaning and use as they have for normal calls. The belt positions or registers are filled with small operand values, in belt order. An argument that is too big to fit in the hardware operands is passed in memory instead. The maximal size for belt or register arguments can be predefined, but all widths of single scalars may be passed by the belt or registers. The belt is of limited fixed size, and the registers are of limited fixed number, so the call may need to pass more belt/register arguments than there are places to put them in; excess arguments are passed in memory instead. By the nature of the belt and registers, all belt/register arguments (and results) are passed-by-copy. The server receives the value of the argument; it does not receive any right to view or modify the source of that value. Similarly, the client receives the value of the result, not the right to view or modify the source of that result.

Arguments that are too big or too numerous are passed in memory, as are variadic arguments (VARARGS or ellipsis arguments, as defined in various languages). In one embodiment, the CPU can use a common protocol for memory arguments to both normal and portal-type call operations. This protocol defines input and output regions of the data stack, where the caller places the arguments in its output region, but after the call the callee sees the same arguments in its input region. The effect of this protocol in a call is that both callee and caller can see and/or modify a memory argument independently and concurrently during the call. Of course, the caller itself is quiescent during the call, but some other thread in the same turf as the caller and running in a different can inspect and modify the arguments while the callee is running in a different core or pre-empted. This concurrent visibility is harmless when caller and callee are trusting, as in a normal call. In a portal-type call operation between a distrustful client and server, the concurrent visibility is unfortunate and potentially exploitable. To avoid problems, all arguments passed in memory for any reason are automatically copied within the server to buffer space that is not visible to the client, before other access. From the view of the called function the access to the passed arguments is the same, and a function may transparently be called either via a portal or via a normal call. However, because arguments are shared in a normal call but unshared in a portal-type call operation, it is possible to write client code that can tell the difference and behaves differently depending on which was used. Such client code necessarily involves concurrent access to the stack locations occupied by the arguments, which is unlikely ever to be needed for client functionality. If concurrent access to memory arguments is ever in fact necessary, then the call signature of the function must be changed to make explicit that the relevant argument is being passed by reference, rather than passedby-observable-value.

In one embodiment, the CPU can support two protocols for pass-by-reference arguments of portal-type call operations: address-based, and index-based. In the address-based protocol, the server receives the actual memory addresses of the arguments, and can use those addresses as ordinary pointers to access the argument data. Code using the address-based protocol for pass-by-reference arguments looks much like code not using a portal, and existing code can be converted into an address-based server with minimal rewrite. However, some software and organizations define their security policy to not only protect the data but also to hide the actual location of the data in memory. Such a policy cannot use the address-based protocol, because the address-