Difference between revisions of "Encoding"

m | |||

| Line 4: | Line 4: | ||

=== <span id="EBB">Extended Basic Block</span> === | === <span id="EBB">Extended Basic Block</span> === | ||

| − | Code on the Mill is organised into <abbr title="Extended Basic Block">EBB</abbr>s, i.e. batches of code with one entry point and one or more exit points. There is no implicit fallthrough in EBBs, the instruction flow can only leave them with an explicit branch, which means at least the last operation in every EBB is | + | [[File:ebb.png|right|alt=EBB overview]] |

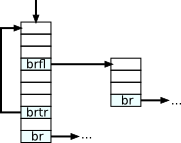

| + | Code on the Mill is organised into <abbr title="Extended Basic Block">EBB</abbr>s, i.e. batches of code with one entry point and one or more exit points. There is no implicit fallthrough in EBBs, the instruction flow can only leave them with an explicit branch, which means at least the last operation in every EBB is an unconditional branch. It can contain more conditional branches that either go to the top of other EBBs or to the top of itself. And in contrast to other architectures there can even be calls in the EBB, they don't leave it, as long as they return normally. The image to the right is a purely logical view. The right block is even a normal canonical basic block with one entry point and one exit. In reality things are a little more complicated, as will be seen later here. | ||

=== <span id="instructions">Instructions and Operations and Bundles</span> === | === <span id="instructions">Instructions and Operations and Bundles</span> === | ||

Revision as of 03:35, 27 July 2014

The Mill architecure employ a unique split stream instruction encoding that though being wide issue and very dense enables sustained decoding rates of over 30 operations per cycle. As it provides those unparalleled numbers, it does so at the fraction of the energy and transistor cost of mainstream variable instruction length instruction sets like x86.

Contents

Semantics

Extended Basic Block

Code on the Mill is organised into EBBs, i.e. batches of code with one entry point and one or more exit points. There is no implicit fallthrough in EBBs, the instruction flow can only leave them with an explicit branch, which means at least the last operation in every EBB is an unconditional branch. It can contain more conditional branches that either go to the top of other EBBs or to the top of itself. And in contrast to other architectures there can even be calls in the EBB, they don't leave it, as long as they return normally. The image to the right is a purely logical view. The right block is even a normal canonical basic block with one entry point and one exit. In reality things are a little more complicated, as will be seen later here.

Instructions and Operations and Bundles

The unusual encoding makes it necessary make clear distincitons between instructions and operations and bundles that are not really necessary on traditional machines. In the earliest RISC architectures an instruction and an operation and a bundle are usually the same thing: a word size bundle of bits is retrieved from the a highest instruction cache line and dropped into the decoder. There one instruction is retrieved and issued resulting in one operation being performed. On wide issue machines one instruction can contain several operations that are all issued together. Modern machines drop a bundle containing several instructions at once into the decoder.

So, a bundle is the batch of memory that gets dropped into the decoder together.

An instruction is all the operations that get issued to the functional units together.

And an operation is the most basic piece of processing in a functional unit, an add or xor for example.

Split Instruction Streams

Bit Format

Rationale

Implementation

See Also

Decode, Phasing, Instruction Set